# 나노임프린트 리소그라피

정건영

# 1. 서론

메모리 집적도는 Moor의 법칙에 따라 18개월마다 두배씩 증가하 는 발전을 보이고 있다. 메모리 집적도는 현대 문명기기의 고 메모리 수요가 늘어남에 따라 더욱 집적화가 요구되어지고 있으며, 이에 따 라 나노 사이즈(100 nm 이하)의 선폭을 기반으로 하는 나노 시대가 도래하였다. 하지만, 기존의 실리콘 반도체 공정에 쓰이는 장비는 나 노 디바이스 구현에 있어서 공정상의 한계 및 막대한 비용의 문제가 있기 때문에 나노 시대를 대비한 새로운 장비 개발 및 공정 개발이 절 실하다. 현재의 반도체 공정의 개발과 메모리 개념은 이러한 소비자 의 요구에 따라가지 못할 것으로 생각되어지며 곧 한계에 도달할 것 으로 예상되어지고 있다.

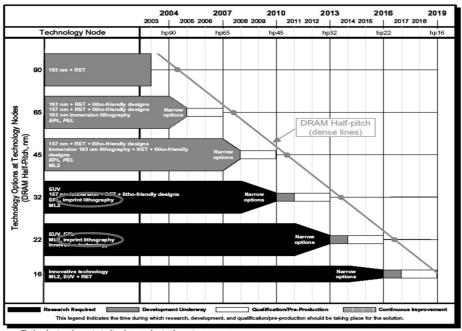

나노임프린트 기법은 1995년 미국 Princeton대학 Chou 박사에 의 해서 처음으로 소개되었으며 현재 나노임프린트 기법은 100 nm 이 하의 선폭을 구현하는 새로운 기법으로 자리매김을 하고 있다.<sup>1</sup> 기존 의 리소그라피는 빛의 파장 한계 그리고, 마스크 재질, 높은 에너지의 광소스가 필요로 하는 문제점이 있지만, 나노임프린트 기법은 공정이 쉽고 간단하고 장비 자체가 현재 반도체 공정에서 쓰이고 있는 광리 소그라피 장비(Deep UV, EUV, X-ray)보다 훨씬 싸다는 장점이 있 다. 임프린트 리소그라피는 2003년 ITRS (International Technology Roadmap for Semiconductors)에 32 nm 이하의 선폭을 실현하는 새로운 리소그라피 장치로 선정되었다(그림 1).2 새롭게 시작된 분야 지만 차세대 리소그라피 장비로 각광을 받고 있으며 여러 연구분야에 서 응용할 수 있어서 많은 연구소와 대학교에서 연구를 수행하고 있다.

## 2. 본론

### 2.1 나노임프린트 공정

나노임프린트 공정은 크게 열에 의한 공정과 UV 조사로 인한 경 화를 통한 패턴 전사 방식이 대표적이다. 우선, 임프린트 공정을 수행 하기 위해서는 요구되어지는 패턴이 표면에서 돌출되어 있는 스탬프 가 필요하다. 나노사이즈의 패턴이 양각되어 있는 스탬프를 제작하기 위해서는 일반적으로 electron-beam lithography와 건식에칭을 통 해 만들어진다.

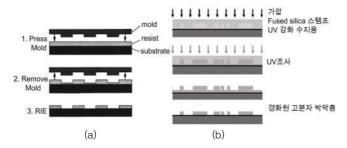

열 나노임프린트의 경우에는 그림 2(a)와 같이 스탬프와 고분자가 캐스팅되어 있는 기판을 접촉시킨 후 열을 주어(보통 고분자의 유리 전이온도(T<sub>d</sub>) 보다 90~100 °C 높게) 고분자의 유동성을 제공한 후, 압력을 주어서 폴리머들이 스탬프의 패턴 사이로 채워지게 함으로써 고분자로의 패턴전사가 이루어지게 한다. 이후  $T_g$  이하로 냉각한 후 스탬프를 고분자 패턴에서 떼어내고 패턴된 하부에 존재하는 잔류층 (residual layer)을 제거함으로써 공정을 마치게 된다. 하지만, 온도 상승과 냉각에 의한 열팽창의 문제점이 내재되어 있기 때문에 다른 재 질의 스탬프와 기판을 접촉 시 열팽창의 차이점으로 인한 임프린트 후 패턴의 찌그러짐과 registration accuracy측면에서 단점을 내재하고 있다. 또한, 초기 단단한 고분자막을 임프린트 하기 위해서는 상대적 으로 높은 임프린트 압력을 주기 때문에 스탬프 표면에 돌출되어 있 는 나노사이즈의 패턴들이 깨질 위험성이 있다.

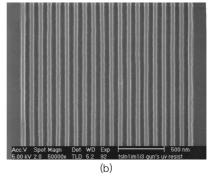

이러한 문제점은 UV를 이용한 임프린트 공정에서 많이 보완될 수 있다. 이 공정은 1996년 Haisma 등에 의해서 처음으로 제안되었으 며<sup>3</sup> 그림 2(b)는 UV 임프린트 공정을 보여준다. 먼저, 기판위에 UV 경화용 리지스트를 캐스팅한 후 스탬프를 누르면 경화용 리지스트 용 액이 스탬프 패턴 사이를 채운다. 점도가 낮기 때문에 낮은 압력에서 도 쉽게 스탬프의 패턴 사이를 채울 수 있다. 이후 UV 광원이 투명한 스탬프를 통해서 리지스트를 감광시키면 리지스트가 경화가 일어나 면서 단단해지게 된다. 이 공정은 상온에서 낮은 압력에서 수행이 가 능하지만, 투명한 석영 스탬프 제작에 어려움이 있다. Electron beam 을 통한 나노 패턴닝 제작시 석영기판이 비전도성이기 때문에 나타 나는 전자의 charging effect로 인해 전자빔의 왜곡을 일으키게 된 다. 또한, 석영을 에칭하는 건식에칭 조건이 잘 잡혀져 있지 못하다. 전자빔의 왜곡을 방지하기 위해서 석영위에 크롬을 얇게 증착하고

1993 1995 2001

1995~ 1996 2001~ 2005 2006~

서강대학교 화학공학과(학사) 서강대학교 화학공학과(석사) Univ. of Durham(UK, 박사)

삼성전자 TFT-LCD 사업부 엔지니어 Hewlett-Packard Labs at Palo Alto,

광주과학기술원 신소재공학과 조교수

#### Nanoimprint Lithography

광주과학기술원 신소재공학과(Gun Young Jung, Department of Materials Science and Engineering, Gwangju Institute of Science and Technology, 261 Cheomdan-gwagiro, Buk-gu, Gwangju 500-712, Korea) e-mail: gyjung@gist.ac.kr

Technologies shown in italics have only single region support.

RET—resolution enhancement technology EUV—extreme ultraviolet

ML2—maskless lithography PEL—proximity electron lithography

그림 1. ITRS roadamp (2003).

그림 2. (a) 열 임프린트 공정 and (b) UV 임프린트 공정 scheme.

전자빔을 이용한 패턴닝을 수행하는 연구가 발표되었다. 이때, 크롬 막은 전자의 charging을 없애주고, 에칭시 마스크로 이용할 수 있는 장점이 있다.<sup>4</sup> 또한, 전도성을 가지는 산화막(indium tin oxide)을 석영이나 유리위에 증착해서 산화막에 패턴닝하는 기술도 발표되었다.<sup>5</sup>

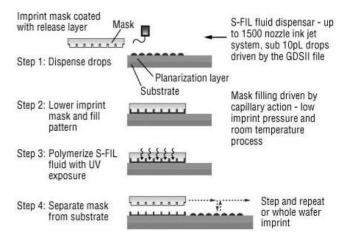

이와 유사한 방법으로 택사스 오스틴 대학 Willson 교수팀은 step and repeat 공정을 제안하였다. 이는 기존의 stepper와 유사한 장비개념으로 reticle과 상응하는 반복적인 패턴을 가지는 스탬프를 이용하며 패턴 전달층이 도포된 기판 위에 UV 경화용 용액을 기판사이에 점적하여 임프린트를 수행한 후, 이동하여 같은 패턴을 반복적으로 웨이퍼 전체에 찍어내는 기술이다. 임프린트 패턴을 에칭마스크로 하여 패턴을 패턴 전달층으로 전사하여 공정을 마치게 된다. 위의 UV 임프린트 공정은 대면적 공정에서 매우 불균일한 잔류층을 형성하고, 다층화 공정 시 전체적으로 정렬을 맞추기 어려워 실제 산업화에 어려움을 내재하고 있다. 그러나, step and repeat 방법을 이용하면 임프린트 면적이 작기 때문에 잔류층 두께 조절이 용이할뿐 아니라 다층화를 위한 정렬이 가능한 장점이 있다.

## 2.2 스탬프

기존의 photo lithography는 마스크의 패턴이 광학 렌즈를 이용하

EPL-electron projection lithography

그림 3. Step and flash imprint 공정(source: www.pennet.com).

여 포토 리지스트 위로 1/4 또는 1/5배로 상이 축소되기 때문에 마스크 패턴은 최종 패턴의 사이즈의 4배 내지 5배로 가능하여 마스크 제작이 상대적으로 용이하다. 그러나, 나노임프린트 공정은 스탬프가 임프린트 리지스트에 직접적으로 맞닿아 패턴전사가 1:1(1X trasfer)로 이루어지기 때문에 스탬프의 패턴 사이즈는 원하는 패턴 사이즈로 정확히 만들어야 한다. 스탬프는 언급한 바와 같이 sequential 공정인전자범을 이용하여 제작하기 때문에 긴 시간을 요한다(경우에 따라서는 1주일이 걸릴 수도 있음). 따라서, 공정단가도 쉽게 접근하기 어려울 정도로 비싸기 때문에 제작된 스탬프는 master 스탬프라 하여 보관하고, 복제공정으로 daughter 스탬프를 만들어서 사용한다. 복제된스탬프를 이용해서 다시 복제가 가능하기 때문에 제작된 제작된 제작된 스탬프를 이용해서 다시 복제가 가능하기 때문에 제작된 master 스탬프로부터 여러개의 복제 스탬프 제작이 용이하다.

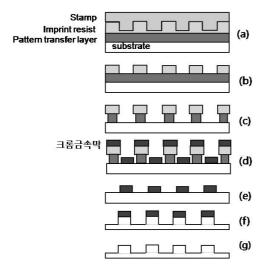

복제는 그림 4와 같이 나노임프린트를 통해서 가능하다. 임프린트

그림 4. 스탬프 복제과정. (a) 임프린트, (b) 스탬프 demolding, (c) 패턴전사층으로 패턴 전달, (d) 금속막 증착, (e) lift-off, (f) 건식삭각, and (g) 금속 마스크가 제거된 복제된 스탬프.

후 패턴 아래에 있는 얇은 잔류층을 제거한다. 그리고, 크롬금속을 중착한 후 lift-off를 통해 패턴된 부분만 크롬금속이 존재한다. 이 크롬금속을 에칭 마스크로 하여 건식에칭을 수행하여 하부 기판(Si, SiO<sub>2</sub>, SiC, silicon nitride, fused silica 등)에 패턴전사가 이루어진다. 이와 같은 공정을 통해 같은 패턴의 복제 스탬프가 제작된다.

더욱 간단한 복제 방법은 임프린트 리지스트가 임프린트 압력을 견디는 기계적 강도가 있다면 이를 바로 스탬프로 적용하는 것이다. Haixiong은 임프린트시 UV를 통한 유리기판 위에 가교된 폴리머 리지스트를 복제 스탬프로 하여 30 nm half-pitch의 패턴전사를 보고하였다. 또한, teflon계열의 수지(AF 2400, Dupont)를 이용하여 복제된 스탬프가 보고되고 있다. 위의 물질은 불소를 기본으로 한 물질로 불활성 성질을 가지고 있어서, 기존의 PDMS가 가지는 낮은 표면에너지를 가지고 있어서 특별한 스탬프 표면 처리를 하지 않고도 바로 임프린트 공정을 수행할 수 있는 장점이 있다. 그리고, PDMS가가지지 못하는 기계적 강도를 가지고 있어서 임프린트 압력을 가할시스탬프 패턴의 찌그러짐을 방지하여 나노사이즈의 패턴 전사도 가능함을 제시하였다.

임프린트 스탬프는 공정을 수행하기 전에 표면처리를 해야 한다. 이 표면 처리는 스탬프 표면을 화학적으로 비활성하게 하여 임프린트 리지스트와의 반응을 방지하고 표면의 표면 에너지를 낮추어서 임프린트된 고분자 패턴에서 잘 띄어지도록 하기 위함이다(releasing property). 불소계열의 단분자막충을 자기조립 방식으로 수용액상에서 또는 기상에서 스탬프 표면에 얹히는 공정을 수행한다. 특별히 나노사이즈의 패턴을 가지는 스탬프를 처리하기 위해서는 기상에서 단분자충을 형성하는 것이 바람직하다. 수용액상에 스탬프를 침하할시패턴과 패턴사이가 나노사이즈인 경우에는 일반적으로 공기가 채워져 수용액이 스탬프 표면과 접촉을 할 수 없기 때문에 releasing 단분자층이 형성이 되지 않는다. 9 따라서, 완벽한 스탬프 표면 처리가되지 않은 경우에는 임프린트후 스탬프 demolding시 고분자 패턴이기판에 붙어있지 않고 스탬프의 패턴사이로 들러붙어버려 패턴닝공정이 실패한다.

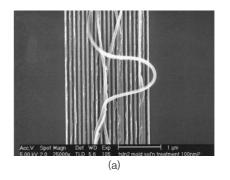

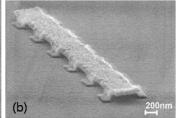

그림 5는 표면 처리가 잘된 스탬프와 그렇지 않은 스탬프를 가지고

그림 5. Demolding후 스탬프 SEM 사진. (a) 수용액상에서 releasing코 팅된 스탬프로 폴리머가 스탬프의 패턴 사이에 달라붙어 있음. (b) 기상에서 코팅된 스탬프로 완벽한 패턴 전사가 이루어졌음.

임프린트한 후 스탬프 표면을 scanning electron microscopy로 본 사진이다. 그림 5(a)와 같이 불완전한 releasing 코팅이 된 스탬프는 임프린트 후 고분자막이 스탬프 패턴 사이에 들러붙어버린 결과이다. 이와 반대로 그림 5(b)는 완벽한 단분자층이 형성될 시에는 스탬프가 임프린트된 고분자층에서 잘 띄어져서 깨끗한 표면을 보여주고 있으며 이는 임프린트 공정이 잘 수행되었음을 보여준다.

#### 2.3 나노임프린트 리지스트

다른 광학을 이용한 리소그라피 방식과 마찬가지로 임프린트 리지스트도 안정적인 임프린트를 수행하기 위해서 많은 특성이 요구되어지고 개발이 필요하다. 낮은 압력에서 쉽게 스탬프의 패턴 사이로 들어가고 또한, 스탬프의 demolding시 깨지지 않고 잘 띄어지는 임프린트 리지스트의 특성이 요구되어진다.

열 임프린트 공정은 초기에 poly (methyl methacrylate)를 이용하여 실험을 수행하였다. 보통 임프린트 온도는 폴리머의 유리전이 온도보다 90도 이상에서 수행한다. 이 온도에서 고분자 물질이 충분한 유동성을 가져서 스탬프 패턴 사이로 채워질 수 있다. PMMA 경우에는 약 200도에서 임프린트를 수행하지만 너무 높은 온도로 인한스탬프와 기판의 열팽창의 불일치와 열순환(가열→냉각)의 긴 공정시간 문제로 낮은 온도에서 수행가능한 리지스트가 요구되어진다. Poly (cyclohexyl acrylate) ( $T_g$ =19 °C)는 100도에서 임프린트 수행이 가능하나 상온보다 낮은 유리전이온도를 가지고 있어서 시간이 지남에 따라 패턴의 형상이 무뎌지는 현상이 관측되었다. 10 또한, 패턴내 잔류 리지스트를 없애는 건식에칭 공정시 reactive ion etching chamber내 온도를 견디지 못하는 낮은 열적 안정성을 가지고 있다.

고분자막의 점도는 유리전이온도 이상에서 온도가 올라감에 따라 낮아져서 쉽게 스탬프의 패턴 사이에 채워지게 됨을 이미 설명하였다.

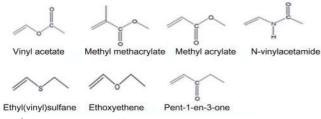

그림 6. 여러 가지 UV 경화용 말단기들.

이 점도는 고분자의 분자량에도 관련이 있다. 고분자의 분자량이 낮으면 고분자 시슬 사이의 얽힘이 작기 때문에 쉽게 외부의 압력에 의해 움직일 수 있다. 그러나, 낮은 얽힘에 의해 기계적 강도가 낮아지는 단점이 있어, 스탬프의 demolding시 임프린트된 패턴이 무너지는 경향을 보인다. 따라서, 구조적으로 안정성을 가지는 임프린트 리지스트는 위에서 언급한 바와 같이 유리전이온도와 분자량을 고려해서 선택하여야 한다.

UV 경화 리지스트는 단량체의 용액이 기본으로 되어 있으며, UV 조사로 경화되어 패턴이 형성된다. 용액 상태이기 때문에 쉽게 스탬 프의 패턴 사이로 스며들어서 낮은 압력에서도 임프린트가 용이하다. 낮은 점도가 특히 요구되어지는데 이는 낮은 압력에서 쉽게 퍼지고 또한, 임프린트 후 패턴내 잔류층의 두께가 거의 없어서 잔류층을 없애는 건식 에칭공정을 없앨 수도 있다. 잔류층을 없애는 건식 에칭공정 정동안 패턴이 옆으로도 또한 삭각되기 때문에 패턴의 분해능이 줄어든다. 따라서, 낮은 점도의 리지스트는 최종적으로 더 좋은 패턴 분해능을 위한 조건이라 할 수 있겠다.

이 뿐 아니라 UV 경화 리지스트가 가져야 할 특성은 다음과 같다. 빠른 경화 속도, 기판과의 좋은 접착력, 스탬프와 잘 띄어지는 낮은 표면 에너지, 기판으로의 패턴 전사를 위한 에칭 저항성 그리고, 높은 기계적 강도 등이 요구되어진다. 이 모든 특성을 구비하기 위해서는 UV 경화 리지스트는 단량체를 기본으로 하고 각각의 특성을 보완해 주는 화학 물질이 혼합되어야 한다. 나노사이즈 패턴을 임프린트하기 위해서는 스탬프의 releasing 표면 처리만으로 충분하지 않기 때문에 리지스트 자체에서도 releasing 특성을 보완해 주어야 한다. 높은 에칭 저항성을 지니기 위해서 실리콘 함량이 많은 단량체를 합성하고 임프린트에 적용하고 있다.<sup>11</sup>

UV 경화 용액의 주성분으로 쓰이는 단량체는 이중결합을 가지는 말단기를 가지고 있으며, **그림 6**은 여러 가지의 말단기를 보여주고 있다. 말단기의 이중결합은 광조사시 광개시제에서 생긴 free radical 과 쉽게 반응하여 단일결합이 되면서 다른 단량체와 반응하고, 이후 연속적인 단량체와의 연쇄반응을 통해 고분자화 된다.

Acrylate와 vinyl—ether 유도물들은 빠른 경화 속도 때문에 UV 경화 용액의 주성분으로 많이 연구되어지고 있다. Acrylate 기반 유도물은 빠른 경화속도 측면에서 좋은 특성이 있지만 산소에 의해 경화가 방해되어 임프린트시 샘플의 가장자리가 경화되지 않는 문제점이보고되었다. Vinyl—ether 유도물은 물과 거의 상등한 점도, acrylate에 버금가는 경화속도 그리고, 산소와 반응하지 않는 좋은 특성을 가지고 있다. 하지만 반응이 빠른 만큼 보관이 용이하지 않고 경화를시작시켜 주는 광개시제와 잘 혼합이 되지 않아 침전되는 문제점이 보고되고 있다. <sup>12</sup> UV 경화 리지스트는 대면적 적용의 측면에서 많은 개발의 여지가 남아 있다.

그림 7. 임프린트로 구현한 3D 구조체. (a) T-gate and (b) air-bridge.

## 2.4 나노임프린트 장 · 단점

지금까지 소개한 나노임프린트는 나노스케일의 디바이스 제작에 획기적인 공정임은 틀림이 없다. 값비싼 전자빔을 이용하지 않으면서도 원본 스탬프만 구비한다면 스탬프를 여러번 복제하여 만들 수 있으며, 대면적도 한번의 프린팅 작업으로 빠른 시간에 작업을 마칠 수있다는 측면에서 차세대 리소그라피 장비로 소개되기도 하였다. 기존의 포토리소그라피는 빛의 회절을 근본으로 한 공정과 현상을 통한패턴 구현이라는 특수성 때문에 패턴의 line edge roughness의 문제를 야기할 수 있다. 점점 작은 패턴을 구현하기 위해서는 파장이 점점 짧은 광원을 개발해야 한다. 이에 반해 UV 임프린트 공정은 물리적인 패턴전사이기 때문에 천문학적 비용이 드는 아주 짧은 파장의 광원의 개발이 필요 없고 또, 빛의 회절에 영향을 받지 않는다는 장점이 있다. 단지, 광개시제의 흡수 파장대의 광원만 필요하다.

또한, 원형의 스탬프를 이용하면 연속적인 roll 기반의 작업이 가능하기 때문에 윤전기와 같이 실시간으로 패턴을 찍어내어 대량생산 측면에서 장점을 가지고 있어 roll-to-roll 임프린트 방식의 연구가 많이 진행되고 있다.

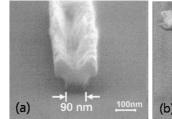

스탬프의 패턴이 3D 구조를 가지고 있다면 한번의 임프런트 공정으로 3D 구조의 패턴을 제작할 수 있는 장점이 있다. 이런 3D 구조는 기존의 포토리소그라피 공정으로는 다수의 lay-out과 포토공정을 통해서 만들어지지만, 임프린트로는 한번의 프린팅으로 구현이 가능하다는 점에서 시간, 비용측면에서 장점이 있다. Mingtao은 한번의임프린트 공정과 lift-off로 그림 7의 40 nm 이하의 T-gate 패턴과 air-bridge의 3차원 구조물을 제작하였다. 13

이러한 장점들에도 불구하고 산업체에서 나노임프린트 공정이 쉽게 기존의 포토 리소그라피 공정을 대체하리라고 생각하지 않는다. 그 이유는 접촉식 공정이기 때문에 아주 작은 particle에도 민감하기 때문이다. 스탬프와 리지스트 사이에 작은 particle이 있다면, 임프린트 후 particle 주위의 패턴은 매우 두꺼운 잔류층을 가지게 된다. 따라서, 이 주위는 금속증착 후 lift-off를 하게 되면 패턴이 남지 않는다. 또한, 작은 particle이라도 스탬프의 나노사이즈 패턴과 맞닿고 압력을 가하게 되면 값비싼 스탬프의 패턴이 영구적으로 깨질 수있기 때문에 매우 주의가 필요하다.

더욱이 디바이스 제작에 있어서 다층공정이 요구되는데 이를 위해서는 미세한 패턴 정렬이 필요하다. 미국의 Molecular Imprint사에서는 정렬 허용도가 10 nm 이하인 Imprio 300 장비를 개발하여 선을 보였다. 14 하지만, 현실적으로 스탬프와 하부 패턴을 정렬하고 압력을 가하면, 스탬프와 기판 사이에 있는 용액 상태의 리지스트가 윤활제역할을 하여 미끄럼 현상이 발생하여 나노 스케일의 정렬 허용도를 가지기가 힘들다. 또한, 프린팅 기법은 같은 사이즈로의 전달이기 때문에 앞서 언급한 바와 같이 스탬프 제작에 있어서 기존의 포토리스그

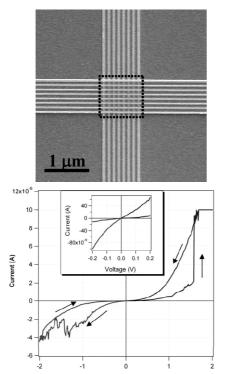

**그림 8.** 8×8 분자 메모리 소자와 1개 셀의 전형적인 I-V 곡선.

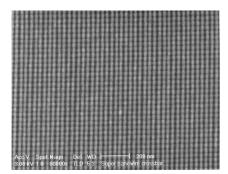

**그림 9.** 17 nm 선폭, 17 nm half-pitch인 금속 나노와이어로 구성된 crossbar 구조.

라피의 reticle 제작보다 어렵고, 경비도 많이 소요된다. 이러한 문제점은 앞으로 장비 개발과 연구를 통해 보완이 된다면 차세대 리소그라피 장비로 각광을 받을 것이다.

# 2.5 나노임프린트 적용

임프린트가 semicoductor IC fab에 적용되기 위해서는 아직까지는 시간당 60-80개의 웨이퍼를 처리할 수 있는 공정 및 장비 개발이 필요하다. 하지만, 공정의 간편성으로 인해 많은 영역에서 이 기술을 이용한 나노 패턴의 적용으로 효율이 높은 디바이스 개발 연구가 진행되고 있다.

미국 Hewlett-Packard사에서는 2003년 차세대 메모리 소자로 나노임프린트를 이용하여 세계 최초의 분자 메모리 소자를 발표하였다. 그림 8은 나노 임프린트 공정을 이용한 제작된 세계 최초의 분자메모리 소자로 8개의 밑전극과 8개의 윗전극 사이에 스위칭 분자가 존재하는 cross-bar 형태를 갖추고 있어, 제작이 간단하고 scalability가 쉽다는 장점이 있다. 이 스위칭 분자에 외부 정전압이임계 전압이상이 걸리면 분자 저항이 현격히 떨어지고(메모리 1), 반대로 어느 이상의 역전압을 걸면 반대로 저항이 급격히 증가하는 현

#### 표 1. 나노임프린트를 이용한 나노 구조체 적용 예

|                 | 연구분야                                                 |

|-----------------|------------------------------------------------------|

| Photonics       | ・반도체 LED(나노사이즈 광결정 구조 제작) <sup>17</sup>              |

|                 | ·유기 LED(pixel 패턴닝) <sup>18</sup>                     |

|                 | · Moth eye 구조 제작(anti-reflection 구조)                 |

|                 | • Wire grid polarizer <sup>19</sup>                  |

|                 | • Optical communication (microring resonator) 20     |

| Patterned media | · High density patterned magnetic media              |

|                 | (25 nm feature size, Samsung, Hitachi) <sup>21</sup> |

| Bio             | · DNA nanofluidic channel <sup>22</sup>              |

|                 | ·나노 구조를 통한 셀 배양 조종 <sup>23</sup>                     |

|                 | · 나노스케일 단백질 패턴닝 <sup>24</sup>                        |

| Electronics     | · 유기 트랜지스터 <sup>25</sup>                             |

|                 | · 실리콘 트랜지스터(60 nm 채널 길이) <sup>26</sup>               |

|                 | • Plastic electronics <sup>27</sup>                  |

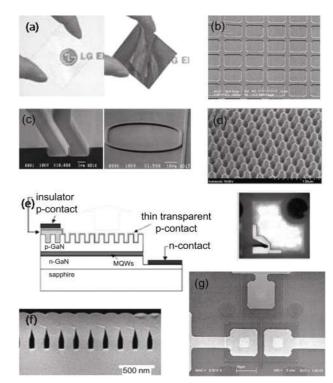

그림 10. 여러분야의 나노임프린트 적용. (a) Wire gird polarizer, (b) LCD pexel 제작, (c) microring rosonator, (d) moth eye 구조, (e) 반도체 LED 광결정 제작(옆그림은 광결정을 통해 나온 빛으로 높은 효율 증가를 이룸), (f) DNA fluidic channel, and (g) 60 nm MOSFET.

어느 이상의 역전압을 걸면 반대로 저항이 급격히 증가하는 현상(메모리 0)을 보이는 메모리의 특성을 보여준다. 이를 이용해서 "Hpinvent"의 문자에 해당하는 ASCII 코드를 각각의 셀에 쓰고 지우기를 반복하여서 분자 메모리 소자의 가능성을 제시하였다. 15

위의 나노와이어의 선폭은 40 nm이며 half-pitch 사이즈는 130 nm이다. 또한, 2005년에는 128개의 17 nm half-pitch 사이즈인 금속선을 나노임프린트 공정으로 cross-bar형태로 제작하였다(그림 9). 이 선폭은 한 개의 머리카락 두께의 만분지 일의 폭을 가질 정도로 아주 작다. 기존의 전자범으로도 이러한 평행한 패턴은 proximity effect 때문에 제작이 불가능하기 때문에 나노임프린트를 수행하기 위한 스탬프는 super lattice 구조를 통하여 제작하였다. 16

표 1과 그림 10은 나노임프린트를 이용한 연구개발을 열거한 것으로 다방면 분야에서 이 기술을 응용하여 나노 구조 접목 및 효율 개선을 보여준 논문들이다. 나노임프린트 공정은 이미 언급한 바와 같이 정렬 허용도의 문제점이 있기에 다층 구조의 디바이스를 제작하기보다는 아직까지는 단층공정(single step)의 적용으로 학계나 산업체에서 연구가 많이 진행되고 있다.

# 3. 결론

나노임프린트 기술은 ITRS road map에 32 nm 이하의 선폭을 구현하는 새로운 리소그라피 공정으로 소개된 새로운 리소그라피 공정이다. 그러나, 산업체에 적용을 위해서는 문제점이 내재되어 있어 이를 극복하기 위한 공정 및 장비개선이 필요하다. 현재 국내 대학의 많은 연구실에서 이 공정을 이용한 디바이스 제작을 구현하고, 산업체에서는 실제로 생산 라인에 투입하기 위한 장비 개발 및 개선의 프로젝트 팀이 운영되고 있다. 임프린트는 나노사이즈의 디바이스를 쉽고 경제적으로 만들 수 있다는 점에서 향후 장비의 수요가늘어날 것으로 예상되어서, 오스트리아 EVGroup, 미국의 Nanonex, Molecular Imprint사, 독일의 Suss Microtech, 일본의 Hitachi 그리고, 한국의 NND사 등 많은 장비업체가 장비개발에 투자하여 차세대 리소그라피 장비로 대체하려고 노력하고 있다.

## 참고문헌

- 1. S. Y. Chou, P. R. Krauss, and P. J. Renstrom, *Appl. Phys. Lett.*, **67**, 3114 (1995).

- ITRS, "International technology roadmap for semiconductors, LITHOGRAPHY", 2003.

- J. Haisma, M. Verheijen, and K. Heuvel, J. Vac. Sci. Technol. B, 14, 4124 (1996).

- T. C. Bailey, D. J. Resnick, D. Mancini, K. J. Nordquist, W. J. Dauksher, E. Ainley, A. Talin, K. Gehoski, J. H. Baker, G. J. Choi, S. Johnson, M. Colburn, M. Meissl, S. V. Sreenivasan, J. G. Ekerdt, and C. G. Willson, *Microelectron. Eng.*, 61, 461 (2002).

- W. J. Dauksher, K. J. Nordquist, D. P. Mancini, D. J. Resnick, J. H. Baker, A. E. Hooper, A. A. Talin, T. C. Bailey, A. M. Lemonds, S. V. Sreennivasan, J. G. Ekerdt, and C. G. Willson, *J. Vac. Sci. Technol. B*, 20, 2857 (2002).

- P. Ruchloeft, M. Colburn, B. Choi, H. Nounu, S. Johnson, T. Bailey, S. Damle, M. Stewart, J. Ekerdt, S. V. Sreenivasan, J. C. Wolfe, and C. G. Willson, *J. Vac. Sci. Technol. B*, 17, 2965 (1999).

- 7. H. Ge, W. Wu, Z. Li, G. Y. Jung, D. Olynick, C. Yuan, S. Y. Wang, and R. S. Williams, *Nano Lett.*, **5**, 179 (2005).

- 8. D. Y. Khang and H. H. Lee, Langmuir, 20, 2445 (2004).

- 9. G. Y. Jung, W. Wu, Z. Li, Y. Chen, S. Y. Wang, W. M. Tong, and R. S. Williams, *Langmuir*, **21**, 1158 (2005).

- 10. L. J. Guo, *J. Phys. D*, **37**, R123 (2004).

- E. K. Kim, N. A. Stacey, B. J. Smith, M. D. Dickey, S. C. Johnson, G. C. Trinque, and C. G. Willson, *J. Vac. Sci. Technol. B*, 23, 2967 (2005).

- 12. C. Decker and D. Decker, *J. Macromol. Sci. Part A: Pure Appl. Chem.*, **34**, 4 (1997).

- 13. M. T. Li, C. Chen, and S. Y. Chou, *Appl. Phys. Lett.*, **78**, 3322 (2001).

- 14. http://www.molecularimprints.com/Products/I300page.html.

- Y. Chen, G. Y. Jung, D. A. A. Ohlberg, X. Li, D. R. Stewart, J. O. Jeppesen, K. A. Nielsen, J. F. Stoddart, and R. S. Williams, Nanotechnology, 14, 462 (2003).

- G. Y Jung, W. Wu, Z. Yu, S.Y. Wang, Z. Li, R. S. Williams, E. Johnston-Halperin, J. E. Green, B. A. Sheriff, A. Boukai, Y. Bunimovich, and J. R. Heath, *Nano Lett.*, 6, 351 (2006).

- 17. S. H. Kim, K. D. Lee, J. Y. Kim, M. K. Kwon, and S. J. Park, *Nanotechnology*, **18**, 55306 (2007).

- 18. X. Cheng, Y. T. Hong, J. Kanicki, and L. J. Guo, *J. Mod. Opt.*, **49**, 663 (2002).

- 19. S. W. Ahn, K. D. Lee, J. S. Kim, S. H. Kim, J. D. S. H. Lee, and P. W. Yoon, *Nanotechnology*, **16**, 1874 (2005).

- 20. C. Y. Chao and L. J. Guo, J. Vac. Sci. Technol. B, 20, 2862 (2002).

- 21. http://www.hitachigst.com/hdd/research/storage/pm/index.html.

- 22. H. Cao, Z. N. Yu, J. Wang, J. O. Tegenfeldt, R. H. Austin, E. Chen, W. Wu, and S. Y Chou, *Appl. Phys. Lett.*, **81**, 174 (2002).

- 23. W. Hu, E. K. F. Yim, R. M. Reano, K. W. Leong, and S. W. Pang, *J. Vac. Sci. Technol. B*, **23**, 2984 (2005).

- 24. J. D. Hoff, L. J. Cheng, E. Meyhofer, L. J. Guo, and A. J. Hunt, *Nano Lett.*, **4**, 853 (2004).

- C. C. Cedeno, J. Seekamp, A. P. Kam, T. Hoffmann, S. Zankovych, C. M. S. Torres, C. Menozzi, M. Cavallini, M. Murgia, G. Ruani, F. Biscarini, M. Behl, R. Zentel, and J. Ahopelto, *Microelectron. Eng.*, 61, 25 (2002).

- 26. W. Zhang and S. Y. Chou, Appl. Phys. Lett., 88, 1632 (2003).

- M. C. McAlpine, R. S. Friedman, and D. M. Lieber, *Nano Lett.*, 3, 443 (2003).